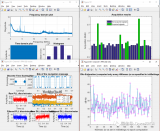

逻辑分析仪是一种电子仪器,可捕获并显示来自数字系统或数字电路的多个信号。逻辑分析仪可以将捕获的数据转....

有时候我们想参考官方的源码,但是有些IP怎么也找不到官方的源码,具体原因是什么呢?

全球导航卫星系统(英文:Global Navigation Satellite System,GNS....

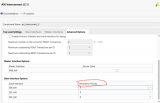

在设计周期中,您可保留多个版本的工程,这些工程使用相同的 IP 和相同的配置。重新运行整个工程会导致....

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)....

fpga 上电时,默认是从 flash 的 0x00 地址开始读数据。如 UG470 文档 page....

鉴于机器学习和人工智能等应用的 FPGA 设计中硬件加速的兴起,现在是剥开几层“云雾”并讨论 HDL....

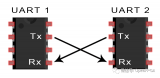

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视....

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视....

自动白平衡模块的设计是使用 HDL Coder 在 MATLAB 和 Simulink 中创建的。H....

最近,CF中某些主播“开(下称KG)挂”升上热搜,作为十年老兵,瓜是吃的饱饱的。之后官方下场进行检测....

我们将使用实例讲解MATLAB / Simulink HDL 使用入门。

该项目通过一个示例演示了 HLS 中组合电路对设计的影响。

用工具用 C 生成 RTL 的代码基本不可读。以下是如何在不更改任何 RTL 的情况下提高设计性能。

Verilog和System Verilog是同一硬件描述语言(HDL)的同义名称。

机器人技术处于工业 4.0、人工智能和边缘革命的前沿。让我们看看如何创建 FPGA 控制的机器人手臂....

核心CPU是XX32FXXX,在工业控制领域其实FPGA占比也很大,所以能不能用FPGA做一个ODr....

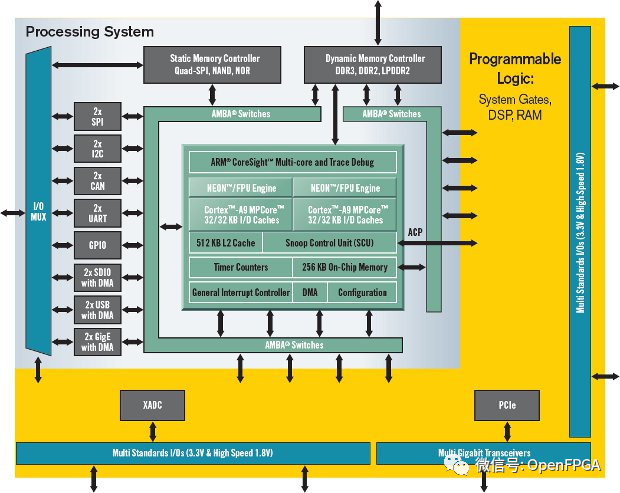

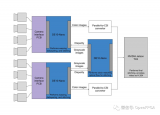

该项目演示如何在 Zynq SoC 上开始使用 FreeRTOS。

虽然想必您知道,在综合或实现阶段,增量运行可以从参考文件中读取和复制信息,但仅在某些阶段中能节省时间....

FPGA设计是无情的,所以我们需要利用能获得的任何软件进行检查

NVM Express ( NVMe ) 或 Non-Volatile Memory Host Co....

我们在Windows系统下使用Vivado的默认设置调用第三方仿真器比如ModelSim进行仿真时,....

AD9144是一款支持jesd204b协议高速DAC芯片。AD9144-FMC-EBZ是基于AD91....

这周末调试《车牌识别算法》遇到点问题,“无聊”中用FPGA搞个2048小游戏玩玩。

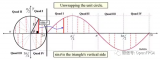

由于某种需求需要生成正弦波,因此使用 C 应用程序中的sin()函数来计算单位圆的幅度值,然后将该幅....

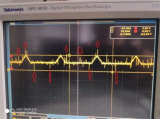

可编程逻辑系统通常部署在可能存在噪声的应用中。这种噪声会影响可编程逻辑设计接收的信号。

本文介绍的是 FPGA VR 相机的第二个版本,第一个版本是下面这样.

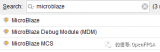

在Block Design中查找IP时输入Microblaze,就会发现下面几种IP,我们常规使用的....

半导体行业中使用范围最广的EDA应用之一。

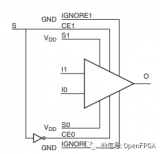

大部分开发者使用 BUFGCTRL 或 BUFGMUX进行时钟切换,它们在时钟切换上可以提供无毛刺输....