Zynq上的非对称多核处理器

Zynq SoC 还拥有大量共享资源,常见示例包括 I/O 外设、片上存储器、中断控制器分配器、L2....

SystemVerilog包的简介与使用

最初的Verilog语言没有一个可用于多个模块的定义。每个模块都必须有任务、函数、常量和其他共享定义....

Vitis HLS的基础知识科普

VitisHLS是一种高层次综合工具,支持将C、C++和OpenCL函数硬连线到器件逻辑互连结构和R....

介绍几个关于ISP算法架构的项目

用python实现的ISP架构,整体项目架构不如OpenISP,但是有几个算法是OpenISP没有的....

匠人精神是怎么用在FPGA存储器

FPGA之所以有这样的能力,是由它本身的结构决定的。比如FPGA有着很强的硬件并行性,能像GPU那样....

SystemVerilog为工程师定义新的数据类型提供了一种机制

为了使源代码更易于阅读和维护,typedef名称应该使用一种命名约定,使名称明显代表用户自定义类型。....

通过无线wifi下载调试fpga的一种方法

上边是整个框图,主要的数据流是Vivado通过PC上的WIFI链接到WIFI路由器上,然后对同一个局....

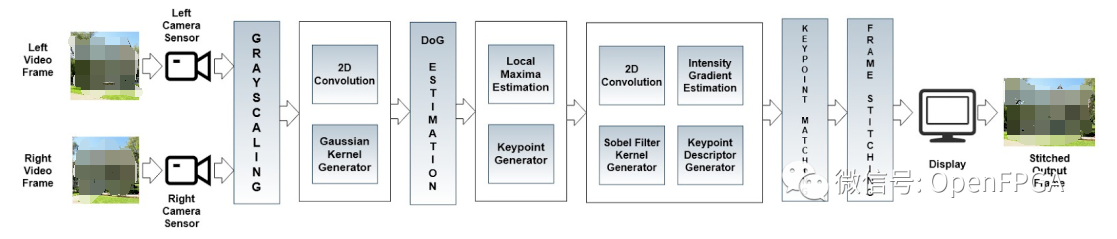

几个视频/图像处理的项目分享

F-I-L是一个FPGA平台的开源的图像处理库,已经拥有了许多常用操作,并在不断更新中。这些操作被以....

使用Xilinx Vivado创建自己板卡文件

board.xml - 定义关于板的所有信息。它包括基本信息(例如电路板名称、描述、供应商)、有关板....

介绍几个脉冲神经网络的开源项目

ODIN 是一种在线学习数字脉冲神经处理器,在 2019 年发表在IEEE Transactions....

网络和变量的未压缩数组

数组的维度定义了数组可以存储的元素总数。未压缩的数组可以用任意数量的维度声明,每个维度存储指定数量的....

DMA控制器介绍及示例演示详解

我们上一节谈到使用 DMA(直接内存访问)的好处已经变得显而易见。到了这一步,我们留下了人类长期以来....

Verilog/FPGA开源项目卷积神经网络

CNN 是多层感知器的正则化版本。多层感知器通常表示全连接网络,即一层中的每个神经元都连接到下一层中....

离散端口的语法和使用指南

SystemVerilog提供用于声明端口列表和端口声明的编码样式:组合样式、传统样式和具有组合类型....

ZYNQ:使用PL将任务从PS加载到PL端

ARM 的 AXI 是一种面向突发的协议,旨在提供高带宽同时提供低延迟。每个 AXI 端口都包含独立....

数字硬件建模SystemVerilog-网络

每个SystemVerilog网络类型都有特定的语义规则,这些规则会影响多个驱动程序的解析方式。虽然....

RTL级的基本要素和设计步骤

顶层设计:RTL设计推荐使用自顶而下的设计方法,因为这种设计方法与模块规划的顺序一致,而且更有利于进....

SystemVerilog常用可综合IP模块库

了解决这个复杂的问题,设计了这个库,它可以帮助您简化设计流程。使用一些简单的 API 可以轻松地在测....

了解Zynq SoC的私有看门狗定时器

每个A9处理器都有私有的32位定时器和32位看门狗定时器。两个处理器共享一个64位定时器。这些定时器....

从算法到RTL实现的问题

我们首先要根据实际需求,针对某方面的信号处理问题,做一个链路级或模块级快速仿真验证设计。最常见的比如....

什么是张量处理单元(TPU)

该项目的目的是创建一个与谷歌的张量处理单元具有相似架构的机器学习协处理器。该实现的资源可定制,可以以....

“软核”硬做-ODrive(FPGA版本)

核心CPU是XX32FXXX,在工业控制领域其实FPGA占比也很大,所以能不能用FPGA做一个ODr....

System Verilog-文本值

文本整数值是一个整数,没有小数点。(IEEE 1800 SystemVerilog标准使用术语“整数....

Perl语言在代码自动生成中的应用实例

Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL语言仅是对已知硬....

Zynq SoC 设备上的多种用途

这篇博文特别关注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模....

SystemVerilog对硬件功能如何进行建模

本文定义了通常用于描述使用SystemVerilog对硬件功能进行建模的详细级别的术语。